86-0755-27838351

以下筆記記錄著振蕩器設計相關的模擬理論

關于晶振的電路布局設置,需要細心的去觀察才能發(fā)現(xiàn)問題所在,專注于電路設計的實際方面設計觀念,石英晶體的對外部電路的阻抗問題校準頻率,晶體等效電路晶振制造商通過水晶產(chǎn)品檢測就會發(fā)現(xiàn)它們之間有沒有存在什么內(nèi)在差異,在現(xiàn)實生活實踐中,你永遠考慮一種振蕩頻率介于兩者之間的晶體共振是平行共振的.反之就是高阻共振,本文文章筆記帶你重新認識石英晶體振蕩器的相關理論知識.

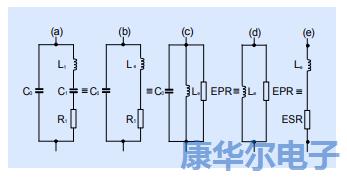

由于a,電流流入B的負載繪制在A處施加的可變頻率的恒壓源下面,在低頻時,石英晶振的運動臂的阻抗是極高的電流隨著頻率的增加而上升C0的電抗降低,到達L1的頻率fr與C1共振,電流急劇上升僅受RL和晶體運動電阻R1的串聯(lián)限制,只在頻率稍高的運動臂表現(xiàn)出增加的凈值感應電抗,在fa處與C0共振,產(chǎn)生電流降到很低的價值,fr和fa之間的區(qū)別是取決于fr和C1到C0的比例,,還是更高頻率,忽略其他晶體振動模式,電流因單獨使用C0而恢復原狀.

任何有源晶體振蕩器的確切頻率取決于相對頻率其中的電壓和電流的相位,并不僅僅是頻率印在水晶上即可,為了振蕩發(fā)生在所需頻率必須有正反饋或零回路相位在那個頻率上轉移,在兩個共振頻率下,晶體"看起來"像電阻一樣施加的電壓和產(chǎn)生的負載電流是同相的,幾乎,由于R1和C0的相對位置,這并非如此等效電路,零相頻率并不完全相同作為最大和最小傳輸?shù)念l率,但在低于100MHz的頻率,其中C0的電抗很高與R1相比,它們可能被認為是這樣的.

大多數(shù)石英晶體振蕩器設計用于在fr處操作晶體出現(xiàn)電阻,或者在fr和fa之間的頻率,讓我們稱之為頻率fL,晶體出現(xiàn)電感,在這種情況下,將晶體電路減少到只有兩個部分:凈電感和等效并聯(lián)或串聯(lián)電阻,我們可以在變換(b)中保持相同的電感值(c)和(d)至(e)因為感應電抗的比例很高由于Q非常高,因此阻力很小,它以相同的頻率(fL)與它共振,就像它與它串聯(lián)一樣,因此,我們留下了高阻值(EPR),或者a低值電阻(ESR),該頻率下的負載電流將為施加電壓的相位.

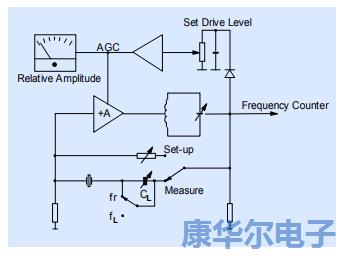

對于必須出現(xiàn)晶體的振蕩器感應我們需要知道有效負載電容是多少由振蕩器電路呈現(xiàn)給晶體,在這種情況下程序是相同的,除了晶體的一系列組合并且該值的電容器僅代替晶體,所有如果這種類型的實際振蕩器電路增加石英晶體電容只有"流浪",并且出于幾個原因建議將其變?yōu)橐粋€工業(yè)標準值為18pF,20pF或30pF,在具有低阻抗,正反饋路徑的調(diào)諧振蕩器中,這可以通過無感可變電阻器來完成通過晶體,如果調(diào)整振蕩器使其頻率和兩條路徑的振蕩幅度相同,那么晶體就會作為其零相頻率Fr和可變電阻振蕩在晶體等效電路中,其值與R1相等.

在實踐中,由于不可避免的雜散電容導致的誤差在貼片晶振和可變電容的連接處,ESR數(shù)字是通常是計算而不是測量,在傳統(tǒng)橋中測量C0之后,值可以是分配給L1,C1和EPR,這是水晶的基礎上面的阻抗計,在大約60MHz以上,晶體C0可以引起非晶體控制振蕩,事實上,如果電抗變得不到一半R1的值,零相位條件不能存在,非常高因此,頻率C0經(jīng)常被平衡或調(diào)出,fL讀數(shù)變得毫無意義,或者,頻率最大傳輸(fM)可以通過其他方式測量.

在網(wǎng)絡系統(tǒng)中,如果晶體有負載,系統(tǒng)會自動鎖定到晶體電容器與串聯(lián),石英晶振具有高精度和可重復性在制造方面提供其他重要優(yōu)勢,只要放大器有足夠的增益來克服由于其輸入引起的損耗,也可以使電路在負載或并聯(lián)諧振器處振蕩如果一個電容等于負載電容的頻率將校準的晶體與晶體串聯(lián)放置,提供方便的手段調(diào)整振蕩器頻率并可用于調(diào)出晶體校準公差.